Progress Report from 12/10/2015 to 19/10/2015

Completed Tasks:

– Study of Gold Sequences and experimentation with Gold Sequence generation algorithms;

– Initialize the development of an RX module architecture for ranging purposes with half pulse-length resolution;

– Initialize the Functional (RTL) simulation of the Ranging measurements functionality (echo detection using transmission lines);

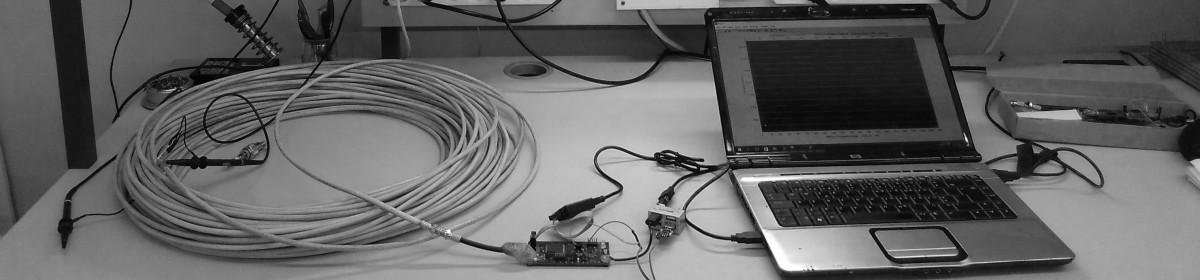

– Development of a simple UART communication protocol between the FPGA hardware and an external control system (laptop) for ranging data logging and plotting.