Progress Report from 05/10/2015 to 12/10/2015

Completed Tasks:

– 2nd meeting with Supervisor;

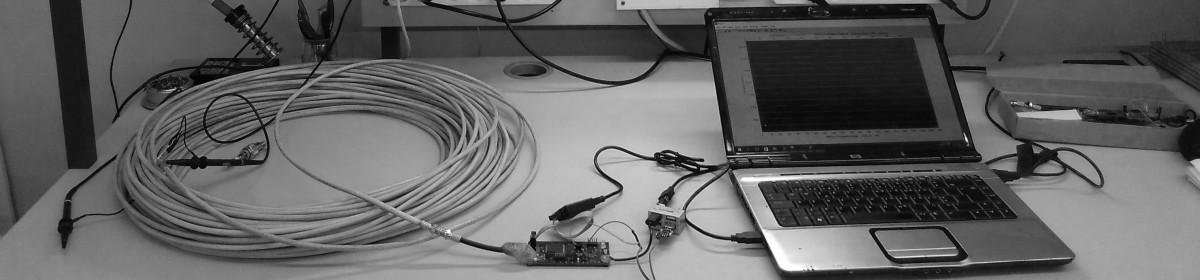

– Deployment of the TX module on FPGA hardware (Altera Cyclone II based board: EP2C5T144);

– Successful demonstration of the TX module functionality: detection of transmitted sequences on a 2nd board at a rate of approximately 3ns per bit (up to 17 bits per symbol, or 17 pulses per chip); Detection without the RX module based on logic comparators (combinational logic);

– Draft of a Ranging configuration scheme for the same FPGA hardware.